| Taiwan Semiconductor Manufacturing Company Limited |

| Registration Date | 5 Sep 2016 |

| Share |

Electronics Electrical Accessories

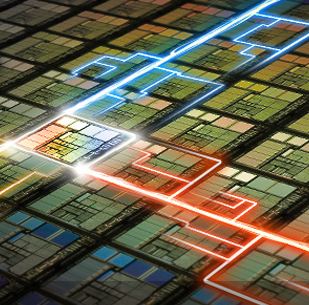

TransistorTSMC's 16FF+ (FinFET Plus) technology can provide above 65 percent higher speed, around 2 times the density, or 70 percent less power than its 28HPM technology. Comparing with 20SoC technology, 16FF+ provides extra 40% higher speed and 60% power saving. By leveraging the experience of 20SoC technology, TSMC 16FF+ shares the same metal backend process in order to quickly improve yield and demonstrate process maturity for time-to-market value. Based on the outstanding FinFET performance improvement, TSMC continues to work with customers for area reduction or low power product enabling. Technology and design innovation keep production costs in check. For example, TSMC can provide both 9T and 7.5T std cells for mobile product chip area and power optimization. Multiple customers' IP have been verified on 16FF+ test chips. 16nm 3D-FinFET structure is different with previous generation planar devices. Empowered by TSMC's Open Innovation Platform® (OIP) design ecosystem, designers can optimize their 16nm designs with qualified IP, design tools and methodologies, including flows for innovative patterning technology. TSMC is supporting both EDA vendors and IP suppliers with design enablement kits. These kits facilitate continuous improvement and interaction between designers, the foundry; and tool and IP suppliers to prepare the 16nm design ecosystem for production success.

TSMC's 16FF+ (FinFET Plus) technology features FinFET transistors with a third generation High-k/Metal Gate process, a fifth generation of transistor strain process, and advanced 193nm lithography. As a result, the 16nm technology offers substantial power reduction for the same chip performance, a must for advanced mobile applications as compared to technologies built with the traditional planar structure.