| Taiwan Semiconductor Manufacturing Company Limited |

| Registration Date | 5 Sep 2016 |

| Share |

Electronics Electrical Accessories

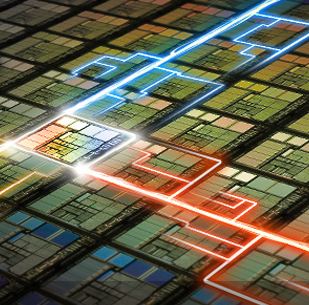

TransistorThe advanced 20nm technology demonstrates double digit 112Mb SRAM yield. The high performance device equipped with second generation gate-last HKMG and third generation Silicon Germanium (SiGe) strain technology. By leveraging the experience of 28nm technology, TSMC's 20nm process can further optimize Backend-of Line (BEOL) technology options and deep collaboration with customers to continue the Moores' Law shrinking path. Technology and design innovation keep production costs in check. In addition, multiple customers' IP have been verified on 20nm test chips. Empowered by TSMC's Open Innovation Platform® (OIP) design ecosystem, designers can optimize their 20nm designs with qualified IP, design tools and methodologies, including flows for innovative patterning technology. Lithography techniques must change at the 20nm node to surmount inherent resolution challenges. TSMC has made this task transparent through our work and collaboration with leading EDA companies. The tools now support built-in technologies that comprehensively cover every design stage for designers to implement 20nm designs with minimum modifications to existing methodologies or flows. TSMC is supporting both EDA vendors and IP suppliers with design enablement kits. These kits facilitate continuous improvement and interaction between designers, the foundry; and tool and IP suppliers to prepare the 20nm design ecosystem for production success.

TSMC's 20nm process technology can provide 30 percent higher speed, 1.9 times the density, or 25 percent less power than its 28nm technology. TSMC 20nm technology is the manufacturing process behind a wide array of applications that run the gamut from tablets and smartphones to desktops and servers.